Yesterday at ICCAD, Jim Hogan and I led an discussion on the megatrends facing electronics and the implications going forward for EDA. Basically we took a leaf out of Scoop Nisker’s book, who when he finished reading the news would sign off with "if you don’t like the news go out and make some of your own." So we tried to.

Yesterday at ICCAD, Jim Hogan and I led an discussion on the megatrends facing electronics and the implications going forward for EDA. Basically we took a leaf out of Scoop Nisker’s book, who when he finished reading the news would sign off with "if you don’t like the news go out and make some of your own." So we tried to.

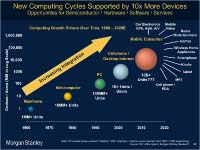

Anyone whose being reading this blog regularly won’t be surprised at the position that we took. I managed to find some interesting data from Morgan Stanley about how electronics is growing but it is also fragmenting. PCs ship in 100s of millions; cell-phones in billions (the world is expected to get to 100% penetration in a couple of years) and the fragmented consumer market in 10s of billions: car electronics, mobile video, home entertainment, games, kindles, iPods, smart-phones and so on.

So the end market is growing strongly but individual systems (with a few exceptions) are shipping in smaller individual volumes.

Meanwhile, over in IC-land the cost of design has been rising rapidly. For a 45nm chip it is now $50M. There are two problems with this for EDA. One is that the sticker price means that a lot fewer chips will be designed, and second that the fastest growing part of the cost is software (where EDA doesn’t play much) now up to almost 2/3 the cost of design. But if a chip costs $50M to design then you’d better be shipping it into a market of 250M+ units or the economics won’t work.

So we have a mismatch: fragmented consumer market requiring low-cost low-volume designs. Semiconductor economics requiring high-cost high-volume designs.

The only way around this is aggregation at the silicon level, along with reconfigurability and reprogrammability.

The most basic form of aggregation is the FPGA, since the basic gates can be used for pretty much any digital design. It’s not very efficient in terms of area or power, but it is completely flexible.

The second form of aggregation is the programmable SoC. This is something I’ve predicted for some time but I was surprised to discover recently that some manufacturers have been building these for several years. Indeed, Cypress gave me a chart showing that they are on track to ship 3/4 billion of this by the end of the year and should pass a billion next year. The programmable SoC doesn’t have completely uncommitted gates like an FPGA, rather it has little building blocks for peripherals, both analog and digital, that can be reconfigured into a wide range of different devices. This can either be done one time to initialize the device, or it can be done dynamically under control of the on-board processor(s).

The third form of aggregation is the platform. This seems to be most successful in the wireless world, TI’s OMAP being the most well-known. But it has also been happening in digital video. At some point it become more efficient to waste silicon by loading up a chip with everything you might ever want, and enable/disable by software, as opposed to eating the huge cost of masks and inventory of specializing each derivative to perfectly match the end customers needs.

Jim carried on to talk about which type of products make money in EDA. There is a range of types of tools from measurement, modeling, analysis, simulation and optimization. The further to the right on this list the more money customers are prepared to pay and the most likely it will be that you can create and sustain a competitive advantage for several years. Each tool needs to be better, faster or cheaper and preferably all three in order to be successful. If you can only have two they’d better be better and faster. Cheaper in EDA has the same connotations as low-cost heart surgeon. With so much on the line that’s not the place to economize.

Ultimately this is moving towards what I call software signoff, the inversion of the way about thinking about electronic systems. Instead of thinking of a complex SoC with some embedded software, a system is actually a big software system, parts of which need to be accelerated by some type of semiconductor implementation to make them economic (fast enough, low enough power). We don’t have the tools today to take complex software and automatically build some parts in gates, assemble IP, assign the software to processors and so on. But that is the direction we need to move in.

The mismatch between fragmented end-markets and high costs of design is potentially disruptive and thus an opportunity to change the way that design is done. I return to Yoshihito Kondo of Sony’s call to arms: "We don’t want our engineers writing Verilog, we want them inventing concepts and transferring them into silicon and software using automated processes."

The presentation is posted on the SI2 website here.