DAC is coming up late July, as I’m sure you know. For the first time this year there is a real user track in which users, unmoderated by EDA marketing droids, can talk about their experiences. Soha Hassoun of Tufts University was the person who didn’t step three paces back fast enough and so found herself volunteered as Design Community chair. Of course, her first question to answer was: what is a design community chair? And the last question, what flavors of ice-cream do users prefer?

DAC is coming up late July, as I’m sure you know. For the first time this year there is a real user track in which users, unmoderated by EDA marketing droids, can talk about their experiences. Soha Hassoun of Tufts University was the person who didn’t step three paces back fast enough and so found herself volunteered as Design Community chair. Of course, her first question to answer was: what is a design community chair? And the last question, what flavors of ice-cream do users prefer?

My design community: the users

It’s three and a half weeks before DAC—and we, the executive committee and organizer MP Associates—are in the final stages of preparing for the User Track at DAC. It’s been a joy ride, with some ups and downs.

I was recruited about a year ago to be the Design Community Chair for DAC. I said I would take the job only if I can re-define what that role means. Andrew Kahng, DAC’s chair, agreed and signed me up.

The questions began: What is a design community? Does it even exist? And, in what forms? How far does it stretch? And, if these design communities already are associated with established conferences, why would they be interested in connecting with DAC? Can we characterize the profile of a typical “design community member”?

Well, after dwelling on these questions for a few days, looking at years’ worth of survey data from DAC, chatting with members of the DAC Executive Committee and many colleagues designing hardware and software, two ideas crystallized. First, DAC in the past has had a hard time identifying with a “design community.” Second, the common characteristic of members of this “design community” was that they “use EDA tools.”

Bingo! That was it. The “design community” label is potentially a mismatch: we were really talking about the “EDA Tool Users.” Relief. At least now we decoded the word “Design” in “Design Community,” and we started talking about “User Community.”

The quest shifted to find a way of connecting a large community, scattered geographically and topically, yet focused on EDA tool use. What would bring members of this EDA User Community to DAC? Certainly not to shop for tools. The user community is much larger than the folks that typically show up at DAC to visit the exhibit floor. The question became, what value can DAC provide to the User Community?

More questions and discussions. Clearly, users would not be willing to spend the time writing length DAC papers, and the user contributions would not be looked upon with enthusiasm considering the main focus of DAC on algorithmic contributions and methodologies.

So, the User Track was born: by users, for users, and chosen by users. We decided on a conference format. The submissions would be shorter. The quality had to be high to attract others. The event would be more inclusive and viewed as a community event to share knowledge and experiences. The event had to offer networking opportunities. Submissions must be evaluated using experts in tool use.

It is now eight months later. We put together a committee of more than 20 super EDA users. We put the word out that we are looking for submissions –– just one page abstracts. We received 117 submissions spanning both front and back end design topics. We accepted about one third as presentations, one third as posters, and one third did not make the quality cut for various reasons.

I’ve already reviewed some of the presentations and posters that will be made at DAC, and they look GREAT. Presenters include users from Infineon Technologies, Cisco, TI, Xilinx, ST Microelectronics, Intel, Virtutech, ClueLogic, ST Microelectronics, Samsung, Qualcomm, Intel, Fujitsu, IBM, Sun, and others.

The User Track is this three-day event with 40 presentations running in parallel with regular technical sessions, and a poster session, held Wednesday 1:30-3 p.m., which provides 42 posters. Did I mention there will be ice cream, too, at the poster session?

Where else can you get such an experience –– the sessions, of course, and not the ice cream? See you there!

Patent law is a controversial subject and keeps popping up unexpectedly (for instance Ron Wilson writes about a case at Applied Materials

Patent law is a controversial subject and keeps popping up unexpectedly (for instance Ron Wilson writes about a case at Applied Materials  Startups have unique problems in human resources. For a start, they don’t have human resource departments or even, in the earliest days, anyone to even do the mechanical stuff of making sure the right forms are filled out. You have to do that yourself.

Startups have unique problems in human resources. For a start, they don’t have human resource departments or even, in the earliest days, anyone to even do the mechanical stuff of making sure the right forms are filled out. You have to do that yourself.

Which came first, the chicken or the egg? This question often gets posed as an example of a question that is impossible to answer, since plainly chickens come from eggs and eggs come from chickens. In EDA, there are chicken and egg business issues: how do you get people to use synthesis when there are no libraries? So then how do you get people to create libraries when nobody uses synthesis? How do you get software engineers to use virtual platforms when the models are not created in advance? And get the component vendors to create the models when the user base is not large enough?

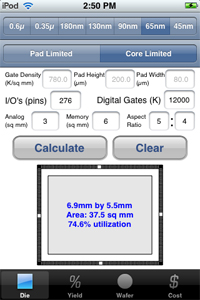

Which came first, the chicken or the egg? This question often gets posed as an example of a question that is impossible to answer, since plainly chickens come from eggs and eggs come from chickens. In EDA, there are chicken and egg business issues: how do you get people to use synthesis when there are no libraries? So then how do you get people to create libraries when nobody uses synthesis? How do you get software engineers to use virtual platforms when the models are not created in advance? And get the component vendors to create the models when the user base is not large enough? One thing that I’ve done in the last few months during my involuntary unemployment, other than writing this blog, has been to teach myself how to program the iPhone. Despite having been in marketing for over a decade, my background is as a software engineer. I wanted to bring my programming skills up to date on a state-of-the-art platform.

One thing that I’ve done in the last few months during my involuntary unemployment, other than writing this blog, has been to teach myself how to program the iPhone. Despite having been in marketing for over a decade, my background is as a software engineer. I wanted to bring my programming skills up to date on a state-of-the-art platform.

Today’s guest blog is Rob Dekker, the President and principal developer at Verific, who produce front-ends used by many EDA tool suppliers both big and small. Prior to founding Verific, Rob was at Exemplar where he was the principal developer of their Leonardo FPGA synthesis product (which was acquired by Mentor in 1995). He started his career at Philips Research in the Netherlands after graduating from Delft University of Technology.

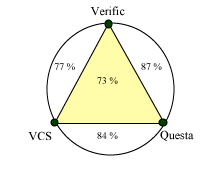

Today’s guest blog is Rob Dekker, the President and principal developer at Verific, who produce front-ends used by many EDA tool suppliers both big and small. Prior to founding Verific, Rob was at Exemplar where he was the principal developer of their Leonardo FPGA synthesis product (which was acquired by Mentor in 1995). He started his career at Philips Research in the Netherlands after graduating from Delft University of Technology. And, then there were situations were either Verific and Questa agreed, or Verific and VCS agreed, but not Questa and VCS. Remember the saying about the person with two watches who never knows what time it is? Well, that’s how we feel in situations like this. Predictably, Questa customers nudge us toward their simulator’s implementation and VCS users like it exactly the other way around. Where does that put us? Between a rock and a hard place!

And, then there were situations were either Verific and Questa agreed, or Verific and VCS agreed, but not Questa and VCS. Remember the saying about the person with two watches who never knows what time it is? Well, that’s how we feel in situations like this. Predictably, Questa customers nudge us toward their simulator’s implementation and VCS users like it exactly the other way around. Where does that put us? Between a rock and a hard place!  I talked earlier about

I talked earlier about  I talked

I talked