It is very rare for a company to develop a new standard and establish it as part of creating differentiation. Usually companies piggy-back their wares on existing standards and attempt to implement them better than the competition in some way. There were exceptions with big companies. When AT&T was a big monopoly it could simply decide what the standard would be for, say, the modems of the day or the plug you phone would use. IBM, when it was an effective monopoly in the mainframe world, could simply decide how magnetic tapes would be written. I suppose Microsoft can just decide what .NET is and millions of enterprise programmers jump.

It is very rare for a company to develop a new standard and establish it as part of creating differentiation. Usually companies piggy-back their wares on existing standards and attempt to implement them better than the competition in some way. There were exceptions with big companies. When AT&T was a big monopoly it could simply decide what the standard would be for, say, the modems of the day or the plug you phone would use. IBM, when it was an effective monopoly in the mainframe world, could simply decide how magnetic tapes would be written. I suppose Microsoft can just decide what .NET is and millions of enterprise programmers jump.

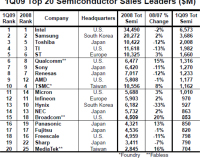

Qualcomm, however, created the basic idea of CDMA, made it workable, owned all the patents, and went from being a company nobody had heard of to being the largest fabless semiconductor company and have even broken into the list of the top 10 largest semiconductor companies.

The firs time I ran across CDMA it seemed unworkable. CDMA stands for code-division multiple access, and the basic technique relies on mathematical oddities called Walsh functions. These are functions that everywhere take either the value 0 or 1 and are essentially pseudo-random codes. But they are very carefully constructed pseudo-random codes. If you encode a data stream (voice) with one Walsh function and process it with another at the receiver you get essentially zero. If you process it with the same Walsh function you recover the original data. This allows everyone to transmit at once using the same frequencies, and only the data stream you are trying to listen to gets through. It is sometimes explained as being like at a nosiy party, and being able to pick out a particular voice by tuning your ear into it.

Years ago I had done some graduate work in mathematics, so I’d actually come across Walsh functions and so the idea of CDMA was very elegant. However, my experience of very elegant ideas is that they get really messy when they meet real-world issues. Force-directed placement, for example, seems an elegant concept but it gets messier once your library cells are not points and once you have to take into account other constraints that aren’t easily represented as springs. So I felt CDMA would turn out to be unworkable in practice. CDMA has its share of complications to the basic elegant underpinning: needing to adjust the transmit power every few milliseconds, needing to cope with multiple reflected, so time-shifted, signals and so on.

At the highest level what is going on is that GSM (and other TDMA/FDMA standards) could get by with very simple software processing since they put a lot of complexity in the air (radio) interface and didn’t make optimal use of bandwidth. CDMA has a very simple radio interface (ignore everyone else) but requires a lot of processing at the receiver to make it work. But Moore’s law means that by the time CDMA was introduced, 100 MIPS digital signal processors were a reality and so it was the way of the future.

Of course, my guess that CDMA was too elegant to be workable was completely wrong. Current and future standards for wireless are largely based on wide-band CDMA, using a lot of computation at the transmitter and, especially, receiver to make sure that bandwidth is used as close to the theoretical maximum as possible.

But before CDMA turned out to be a big success Qualcomm was struggling. In about 1995 VLSI tried to license CDMA to be able to build CDMA chips as well as the GSM chips that they already built. Qualcomm had “unreasonable” terms and were hated in the industry since they charged license fees to people who licensed their software, people who built phones (even if all the CDMA was in chips purchased from Qualcomm themselves) and people who built chips (even if they only sold them to people who already had a Qualcomm phone license). They were hated by everyone. Now that’s differentiation. The royalty rates were too high for us and we ended up walking from the deal.

I was in Israel 2 days from the end of a quarter when I got a call from Qualcomm. They wanted to do a deal. But only if all royalties were non-refundably pre-paid up front in a way they could recognize that quarter. Sounds like an EDA license deal! We managed to do a deal on very favorable terms (I stayed up all night two nights in a row, after a full day’s work, since I was 10 hours different from San Diego, finally falling asleep before we took off from Tel Aviv and having to be awakened after we’d landed in Frankfurt). The license was only about $2M or so in total I think, but that was the relatively tiny amount Qualcomm needed to avoid having a quarterly loss and impacting their stock price and so their ability to raise the funds that they would need to make CDMA a reality. Which they proceeded to do.

I see a fair number of EDA startups. Most of them have some potentially innovative technology that solves a problem that is getting or going to get worse at future process nodes. But it is really hard to assess whether the technology works well, whether it will work on the type of designs that will be done in the future, and whether the approach will turn out to form a sizeable market. At the last few jobs I did I had to work as a consultant for a time before I could even assess whether the technology was good enough to want to sign onto the company.

I see a fair number of EDA startups. Most of them have some potentially innovative technology that solves a problem that is getting or going to get worse at future process nodes. But it is really hard to assess whether the technology works well, whether it will work on the type of designs that will be done in the future, and whether the approach will turn out to form a sizeable market. At the last few jobs I did I had to work as a consultant for a time before I could even assess whether the technology was good enough to want to sign onto the company.

San Francisco is a dormitory town for Silicon Valley. Not completely, of course. But unless you regularly drive between Mountain View and San Francisco you probably aren’t aware of the huge fleet of buses that now drives people from San Francisco to other cities: Google in Mountain View, Yahoo all over, Genetech in South San Francisco, Ebay in San Jose. I have a friend who knows Gavin Newsom, the mayor, and keeps trying to get him to come and stand on a bridge over the freeway one morning to see just what is happening where lots of people (me included) largely work in Silicon Valley but live in the city. The traffic is still more jammed entering the city than leaving but it’s getting close. Bauer, who used to just run limos I think, now has a huge fleet of buses with on-board WiFi that they contract out to bring employees down to the valley from San Francisco. They cram the car-pool lane between all those Priuses making the not-so-green 40 mile trip.

San Francisco is a dormitory town for Silicon Valley. Not completely, of course. But unless you regularly drive between Mountain View and San Francisco you probably aren’t aware of the huge fleet of buses that now drives people from San Francisco to other cities: Google in Mountain View, Yahoo all over, Genetech in South San Francisco, Ebay in San Jose. I have a friend who knows Gavin Newsom, the mayor, and keeps trying to get him to come and stand on a bridge over the freeway one morning to see just what is happening where lots of people (me included) largely work in Silicon Valley but live in the city. The traffic is still more jammed entering the city than leaving but it’s getting close. Bauer, who used to just run limos I think, now has a huge fleet of buses with on-board WiFi that they contract out to bring employees down to the valley from San Francisco. They cram the car-pool lane between all those Priuses making the not-so-green 40 mile trip. I talked

I talked

About 12 years ago I went on a three-day seminar about the wireless industry presented by the wonderfully named Herschel Shosteck (who unfortunately died of cancer last year although the company that bears his name still runs similar workshops). It was held at an Oxford college and since there were no phones in the rooms, they didn’t have a way to give us wake-up calls. So we were all given alarm clocks. But not a modern electronic digital one. We were each given an old wind-up brass alarm clock. But there was a message behind this that Herschel had long espoused: old standards live a lot longer than you think and you can’t ignore them and hope that they will go away.

About 12 years ago I went on a three-day seminar about the wireless industry presented by the wonderfully named Herschel Shosteck (who unfortunately died of cancer last year although the company that bears his name still runs similar workshops). It was held at an Oxford college and since there were no phones in the rooms, they didn’t have a way to give us wake-up calls. So we were all given alarm clocks. But not a modern electronic digital one. We were each given an old wind-up brass alarm clock. But there was a message behind this that Herschel had long espoused: old standards live a lot longer than you think and you can’t ignore them and hope that they will go away. My favorite old standard is the automobile “cigarette lighter” outlet. According to Wikipedia it is actually a

My favorite old standard is the automobile “cigarette lighter” outlet. According to Wikipedia it is actually a  that only a handful of big companies used, and planes were too expensive for ordinary people. Talking of planes, why do we always get on from the left-hand side? Because it is the "port" side that ships would put against the port for loading, unobstructed by the steering-oar that was on the right-hand side before the invention of the rudder, hence steer-board or "starboard". The first commercial planes were sea-planes, so they naturally followed along. Another old standard lives on, a thousand years after steering-oars became obsolete.

that only a handful of big companies used, and planes were too expensive for ordinary people. Talking of planes, why do we always get on from the left-hand side? Because it is the "port" side that ships would put against the port for loading, unobstructed by the steering-oar that was on the right-hand side before the invention of the rudder, hence steer-board or "starboard". The first commercial planes were sea-planes, so they naturally followed along. Another old standard lives on, a thousand years after steering-oars became obsolete. Customer support in an EDA company goes through three phases, each of which actually provides poorer support than the previous phase (as seen by the long-term customer who has been there since the beginning) but which is at least scalable to the number of new customers. I think it is obvious that every designer at a Synopsys customer who has a problem with Design Compiler can’t simply call a developer directly, even though that would provide the best support.

Customer support in an EDA company goes through three phases, each of which actually provides poorer support than the previous phase (as seen by the long-term customer who has been there since the beginning) but which is at least scalable to the number of new customers. I think it is obvious that every designer at a Synopsys customer who has a problem with Design Compiler can’t simply call a developer directly, even though that would provide the best support.

DAC has just announced the program. You probably already know, but just in case you don’t: DAC is late this year, July 26-31st and it is in San Francisco at the Moscone Center (walking distance from where I live, yeah!). The DAC website is at

DAC has just announced the program. You probably already know, but just in case you don’t: DAC is late this year, July 26-31st and it is in San Francisco at the Moscone Center (walking distance from where I live, yeah!). The DAC website is at