There are two classes of true 3D chips which are being developed today. The first is known as 2½D where a so-called silicon interposer is created. The interposer does not contain any active transistors, only interconnect (and perhaps decoupling capacitors), thus avoiding the issue of threshold shift mentioned above. The chips are attached to the interposer by flipping them so that the active chips do not require any TSVs to be created. True 3D chips have TSVs going through active chips and, in the future, have potential to be stacked several die high (first for low-power memories where the heat and power distribution issues are less critical).

There are two classes of true 3D chips which are being developed today. The first is known as 2½D where a so-called silicon interposer is created. The interposer does not contain any active transistors, only interconnect (and perhaps decoupling capacitors), thus avoiding the issue of threshold shift mentioned above. The chips are attached to the interposer by flipping them so that the active chips do not require any TSVs to be created. True 3D chips have TSVs going through active chips and, in the future, have potential to be stacked several die high (first for low-power memories where the heat and power distribution issues are less critical).

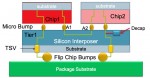

The active die themselves do not have any TSVs, only the interposer. This means that the active die can be manufactured without worrying about TSV exclusion zones or threshold shifts. They need to be microbumped of course, since they are not going to be conventionally wire-bonded out. The picture at the head of this post shows (not to scale, of course) the architecture; click on the thumbnail for a larger image.

The image shows two die bonded to a silicon interposer using microbumps. There are metal layers of interconnect on the interposer, and TSVs to get through the interposer substrate to be able to bond with flip chip bumps to the package substrate. Flip-chip bumps are similar to micobumps but are larger and more widely spaced.

So is anyone using this in production yet? It turns out that Xilinx is using this for their Virtex-7 FPGAs. They call the technology “stacked silicon interconnect” and claim that it gives them twice the FPGA capacity at each process node. This is because very large FPGAs only become viable late after process introduction when a lot of yield learning has tak en place. Earlier in the lifetime of the process, Xilinx have calculated, it makes more sense to create smaller die and then put several of them on a silicon interposer instead. It ends up cheaper despite the additional cost of the interposer because such a huge die would not yield economic volumes.

en place. Earlier in the lifetime of the process, Xilinx have calculated, it makes more sense to create smaller die and then put several of them on a silicon interposer instead. It ends up cheaper despite the additional cost of the interposer because such a huge die would not yield economic volumes.

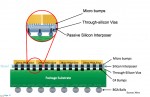

The Xilinx interposer consists of 4 layers of 65um metal on a silicon substrate. TSVs through the interposer allow this metal to be connected to the package substrate. Microbumps allow 4 FPGA die to be flipped and connected to the interposer. See the picture to the right. An additional advantage of the interposer is that it makes power distribution across the whole die simpler.

This seems to be the only design in high volume production, at least at the conference this was the example that every speaker seemed to use.