I’ve talked before about just how amazing Apple’s performance in the cell-phone (and laptop) market is. Last quarter, only two years after entering the cell-phone market, Apple became #1, at least if you measure by how much money they made rather than how many phones they shipped.

I’ve talked before about just how amazing Apple’s performance in the cell-phone (and laptop) market is. Last quarter, only two years after entering the cell-phone market, Apple became #1, at least if you measure by how much money they made rather than how many phones they shipped.

Apple shipped 7.4 million iPhones for $4.5 billion but they made more profit on them than Nokia made on the 108.5 million phones they shipped for $10.36 billion. Strategy Analytics estimated (since Apple doesn’t tell) that Apple made a profit of $1.6 billion whereas Nokia made only $1.1 billion.

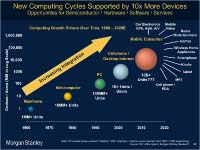

I had a slide from Morgan Stanley at the ICCAD meeting last week that showed that iPhone is the fastest ever adoption of a consumer electronics technology. Actually, that’s not really fair since Apple waited until the market already existed unlike, say, RIM (blackberry) who had to create the market for smart-phones. But Apple has executed flawlessly so far.

Of course there is a big patent battle going on since it is impossible to build a cell-phone without infringing lots of patents held by lots of different parties. Indeed, when I was at VLSI I got involved in patents that we might be infringing. Patents were divided by the industry into essential and non-essential. An essential patent was one that you had to infringe to build a conforming GSM handset. For example, Philips owned a patent on the specific parameters used in the voice compression algorithm GSM adopted and they wanted, I think, $1 per phone license fee. Unsurprisingly Nokia owns lots of patents on cell-phone technology so thinks that Apple should pay them a license fee on all those iPhones as, I’m sure, do dozens of other people (the iPhone is GSM technology, although a universal iPhone that also supports CDMA is rumored to be coming).

The Motorola Droid came out this week too. I’ve not used one so I don’t have much to say but one thing that it has (free) that iPhone does not is turn-by-turn directions when driving. I hadn’t realized that Google had built up their own turn-by-turn database because they didn’t want to pay high royalties for map data. Then they said sayonara to Navteq (acquired by Nokia for $8.1 billion) and Tele Atlas (acquired by Tom Tom for $2.7 billion). Apple doesn’t have their own map database and if you want turn-by-turn directions on the iPhone then “there’s an app for that” and Tom Tom will sell you one for $99.99. It will be interesting to see how this particular little corner of cell-phone space plays out.

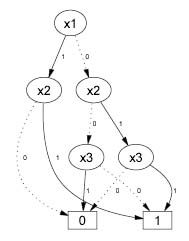

Last week was the EDAC Kauffman Award dinner. One minor advantage of being a blogger is that I got invited along as press. “Will blog for food”. This year’s winner was Professor Randal Bryant, usually just known as Randy Bryant.

Last week was the EDAC Kauffman Award dinner. One minor advantage of being a blogger is that I got invited along as press. “Will blog for food”. This year’s winner was Professor Randal Bryant, usually just known as Randy Bryant.

I spent part of last Tuesday at the Cadence mixed-signal workshop. I went mainly out of interest to see how things had progressed since I worked at Cadence. I had been put in charge of what we called the Superchip project, which was actually integrating together the custom design and the digital synthesis, place & route design to get them into a single design environment. The heart of the problem was to get both systems onto a single database for mixed signal design. This turned out to be immensely complicated since the basic semantics of the two design databases were so different, and nobody in the company had a deep understanding of both of them.

I spent part of last Tuesday at the Cadence mixed-signal workshop. I went mainly out of interest to see how things had progressed since I worked at Cadence. I had been put in charge of what we called the Superchip project, which was actually integrating together the custom design and the digital synthesis, place & route design to get them into a single design environment. The heart of the problem was to get both systems onto a single database for mixed signal design. This turned out to be immensely complicated since the basic semantics of the two design databases were so different, and nobody in the company had a deep understanding of both of them. I caught up with Dave Stewart and Skip Hovsmith of CriticalBlue (from Edinburgh, yay, one of my alma maters). They originally developed technology to take software and pull it out of the code and implement it in gates. They had some limited success with this. But now they have refocused their technology on the problem of taking legacy code and helping make it multicore ready with their Prism tool.

I caught up with Dave Stewart and Skip Hovsmith of CriticalBlue (from Edinburgh, yay, one of my alma maters). They originally developed technology to take software and pull it out of the code and implement it in gates. They had some limited success with this. But now they have refocused their technology on the problem of taking legacy code and helping make it multicore ready with their Prism tool. I went to Mike Muller’s keynote at ARM’s techcon3. He started with an interesting retrospective on ARM. They have shipped 15B units (4B in 2008 alone). They have 20+ processor cores, 600+ licensees. In the next 3 or 4 years they will ship another 15B units. It’s not far off to say that “almost all” microprocessors are ARMs (by unit count).

I went to Mike Muller’s keynote at ARM’s techcon3. He started with an interesting retrospective on ARM. They have shipped 15B units (4B in 2008 alone). They have 20+ processor cores, 600+ licensees. In the next 3 or 4 years they will ship another 15B units. It’s not far off to say that “almost all” microprocessors are ARMs (by unit count). I was at the ARM developer conference this week. Actually it has been renamed and is now called Techcon3, which seems pretty generic as branding. Anyway, one of the keynotes was by TJ Rodgers who started off by telling us more than we wanted to know about how he is using software and hardware to try and make the new world’s best pinot noir (he’s conceded that DRC is too hard to beat, but that’s old world). However, there was a serious point: he used Cypress PSoCs (programmable systems on chip) to implement the hardware, which was a use not envisaged when the hardware was designed.

I was at the ARM developer conference this week. Actually it has been renamed and is now called Techcon3, which seems pretty generic as branding. Anyway, one of the keynotes was by TJ Rodgers who started off by telling us more than we wanted to know about how he is using software and hardware to try and make the new world’s best pinot noir (he’s conceded that DRC is too hard to beat, but that’s old world). However, there was a serious point: he used Cypress PSoCs (programmable systems on chip) to implement the hardware, which was a use not envisaged when the hardware was designed.